# XA-XTAG4 DATASHEET

XM-014675-DS

2022-10-05

### IN THIS DOCUMENT

- Introduction

- XTAG Block Diagram

- XU316-1024-QF60A device

- Status Indicators

- xSYS2 Connector (J4)

- Debug Cable

- Further information

#### **INTRODUCTION**

The XA-XTAG4 debug adapter allows load, run and debug of firmware on XMOS processors. Connection to the host, running the XMOS XTC development tools, is via USB, connection to the target is via the xSYS2 interface.

The xcore-200 and xcore.ai target devices are supported.

The diagram below shows the layout of the components on the card.

Fig. 1: XA-XTAG4 board

To debug a board with the XA-XTAG4 you must use XTC Tools 15.1 or later, available from the XMOS website: <u>https://www.xmos.ai/software-tools/</u>

The target board should have an XMOS xSYS2 connector fitted. Details of the this connector can be found in the XU316 datasheets.

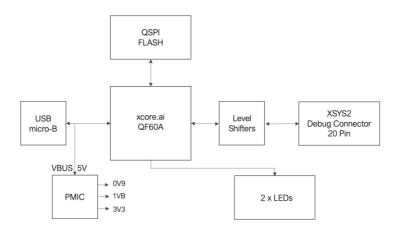

## XTAG BLOCK DIAGRAM

# XU316-1024-QF60A DEVICE

The XA-XTAG4 is based on the XU316-1024-QF60A device comprising two xCORE tiles comprising a multicore microcontroller with tightly integrated general purpose I/O pins and 1024 KBytes of on-chip RAM. The firmware configures the device as a high speed USB device with data connections to the target through JTAG and the XSCOPE XMOS Link.

# STATUS INDICATORS

Two LEDs on the XTAG are driven by the debugger POWER and STATUS with their function shown below:

#### POWER indicator:

| INDICATION | MEANING                                        |

|------------|------------------------------------------------|

| Green      | xtag is powered up and firmware is running     |

| Off        | xtag is unpowered or downloading xtag firmware |

#### STATUS indicator:

| INDICATION | MEANING                                      |

|------------|----------------------------------------------|

| Green      | Connected and xcores are running             |

| Amber      | Connected and xcores are in their debug mode |

| Off        | No current xgdb/xrun connection to target    |

# XSYS2 CONNECTOR (J4)

The XA-XTAG4 includes an xSYS2 20-way IDC header, which can be used to connect it to an XMOS development board for debugging programs on the hardware.

The signals interfacing to the target are split into two groups, JTAG and LINK. Each group can have different signalling levels as defined by the voltage on the VREF\_JTAG and VREF\_LINK pins which are sourced from the target board. xcore-200 devices should use 3.3V for both groups. xcore.ai devices should use 1.8V for the JTAG group and 1.8V or 3.3V for the LINK group dependent on the target hardware.

| PIN<br>NO | SIGNAL<br>NAME | DIRECTION | ASSOCIATE<br>D VREF | DESCRIPTION |

|-----------|----------------|-----------|---------------------|-------------|

|-----------|----------------|-----------|---------------------|-------------|

| 1                            | VREF_JTAG    | Target to xtag | -         | Voltage reference for JTAG, Reset<br>and GPIO. This is the interfacing<br>voltage level used for the JTAG<br>interface. Must be provided by the<br>target board. 0.8V to 3.6V. |

|------------------------------|--------------|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                            | TMS          | xtag to Target | VREF_JTAG | JTAG Test Mode Select signal to the target.                                                                                                                                    |

| 4                            | ТСК          | xtag to Target | VREF_JTAG | JTAG Test Clock signal to the target.                                                                                                                                          |

| 6                            | TDO          | Target to xtag | VREF_JTAG | JTAG Test Data Output from the target.                                                                                                                                         |

| 8                            | TDI          | xtag to Target | VREF_JTAG | JTAG Test Data Input signal to the target.                                                                                                                                     |

| 10                           | RST_N        | Output         | VREF_JTAG | Reset signal to the target. Active Low.<br>Open-Drain. This is also sampled by<br>the xtag to sense if the target is in<br>reset.                                              |

| 11                           | VREF_LINK    | Target to xtag | -         | Voltage reference for the XMOS Link<br>(used for xScope). Must be provided<br>by the target board. 0.8V to 3.6V.                                                               |

| 12                           | XL_DN1       | xtag to Target | VREF_LINK | Downstream (from xtag) XMOS link wire 1.                                                                                                                                       |

| 14                           | XL_DN0       | xtag to Target | VREF_LINK | Downstream (from xtag) XMOS link wire 0.                                                                                                                                       |

| 16                           | XL_UP0       | Target to xtag | VREF_LINK | Upstream (to xtag) XMOS link wire 0.                                                                                                                                           |

| 18                           | XL_UP1       | Target to xtag | VREF_LINK | Upstream (to xtag) XMOS link wire 1.                                                                                                                                           |

| 20                           | GPO          | Output         | VREF_JTAG | Multipurpose GPIO. Open-Drain.                                                                                                                                                 |

| 3,5,7,<br>5,17, <sup>-</sup> | 9,13,1<br>19 | GND            | `GND      | Signal/Power Ground.                                                                                                                                                           |

The interface can also be used with a smaller 10 pin connector which only connects pins 1-10. This does not connect the XMOS link so does not have xScope functionality. See the XU316 datasheet for futher information.

# XSYS2 CABLE

A ribbon cable is required for connection to the target board. The connector on the XTAG4 accepts a 20 way, 0.05"/1.27mm pitch connector An appropriate length is 150mm.

Fig. 3 – Debug adapter cable

A suitable cable assembly can be obtained from DigiKey:

https://www.digikey.com/product-detail/en/harwin-inc/M50-9101042/952-2662-ND/3922577

## FURTHER INFORMATION

|                       | LINK                                      |

|-----------------------|-------------------------------------------|

| XU316 (xcore.ai)      | https://www.xmos.ai/xcore-ai/             |

| XTC Tools User Guide  | https://www.xmos.ai/file/tools-user-guide |

| XTC Programming Tools | https://www.xmos.ai/software-tools        |

## **REVISION HISTORY**

| DOCUMENT VERSION | RELEASE DATE | CHANGE DESCRIPTION |

|------------------|--------------|--------------------|

| XM-014675-DS-1   | 2022-07-13   | First Release      |

|                  |              |                    |

|                  | 1            | I                  |

Copyright © 2022 XMOS Ltd, All Rights Reserved.

XMOS Ltd is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS, VocalFusion and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.