# lib\_spi: SPI Library

Publication Date: 2025/9/12

Document Number: XM-006232-UG v4.0.0

#### IN THIS DOCUMENT

| 1  |           |                |                                         |  |  |  |

|----|-----------|----------------|-----------------------------------------|--|--|--|

| 2  |           |                | ents                                    |  |  |  |

|    | 2.1       | SPI Master (S  | ,                                       |  |  |  |

|    | 2.2       | SPI Master (A  | synchronous)                            |  |  |  |

|    | 2.3       |                |                                         |  |  |  |

| 3  | SPI Mod   | es             |                                         |  |  |  |

|    | 3.1       | Mode 0 - CPO   | L: 0 CPHA 0                             |  |  |  |

|    | 3.2       | Mode 1 - CPO   | L: 0 CPHA 1                             |  |  |  |

|    | 3.3       | Mode 2 - CPO   | L: 1 CPHA 0                             |  |  |  |

|    | 3.4       | Mode 3 - CPO   | L:1CPHA1                                |  |  |  |

| 4  | External  |                | otion                                   |  |  |  |

| 5  |           |                | ore SPI master                          |  |  |  |

| _  | 5.1       | 9              | ster data lines                         |  |  |  |

| 6  |           |                |                                         |  |  |  |

| 0  | 6.1       | 3              |                                         |  |  |  |

| 7  |           |                | e data lines                            |  |  |  |

| /  | 7.1       | -              |                                         |  |  |  |

|    | 7.1       | ,              |                                         |  |  |  |

|    | 7.0       | 7.1.1          | Synchronous master usage state machine  |  |  |  |

|    | 7.2       |                | synchronous operation                   |  |  |  |

|    |           | 7.2.1          | Asynchronous master command buffering   |  |  |  |

|    |           | 7.2.2          | Asynchronous master usage state machine |  |  |  |

|    | 7.3       |                | ransaction gap                          |  |  |  |

| 8  | Slave us  | 9              |                                         |  |  |  |

| 9  |           |                | racteristics                            |  |  |  |

|    | 9.1       | Synchronous    | SPI master clock speeds                 |  |  |  |

|    | 9.2       | Asynchronous   | s SPI master clock speeds               |  |  |  |

|    | 9.3       | MISO port tim  | ing                                     |  |  |  |

| 10 | SPI slave | e timing chara | acteristics                             |  |  |  |

| 11 | Example   | S              |                                         |  |  |  |

|    | 11.1      | SPI Master Ex  |                                         |  |  |  |

|    |           | 11.1.1         | Overview                                |  |  |  |

|    |           | 11.1.2         | Declaring ports                         |  |  |  |

|    |           | 11.1.3         | The application main() function         |  |  |  |

|    |           | 11.1.4         | The app() task                          |  |  |  |

|    |           | 11.1.5         | Building                                |  |  |  |

|    |           | 11.1.6         | Running                                 |  |  |  |

|    | 11.2      | SPI Slave Exa  | 5                                       |  |  |  |

|    | 11.2      |                | ·                                       |  |  |  |

|    |           | 11.2.1         | Overview                                |  |  |  |

|    |           | 11.2.2         | Declaring ports                         |  |  |  |

|    |           | 11.2.3         | The application main() function         |  |  |  |

|    |           | 11.2.4         | The reg_file() task                     |  |  |  |

|    |           | 11.2.5         | The app() task                          |  |  |  |

|    |           | 11.2.6         | The tester() task                       |  |  |  |

|    |           | 11.2.7         | Building                                |  |  |  |

|    |           | 11.2.8         | Running                                 |  |  |  |

| 12 |           | e Usage        |                                         |  |  |  |

| 13 | API Refe  | erence         |                                         |  |  |  |

|    | 13.1      | Master API .   |                                         |  |  |  |

|    |           | 13.1.1         | Supporting types                        |  |  |  |

|    |           | 13.1.2         | Creating an SPI master instance         |  |  |  |

|    |           | 13.1.3         | SPI master interface                    |  |  |  |

|    |           | 13.1.4         | SPI master asynchronous interface       |  |  |  |

|    | 13.2      | Slave API      |                                         |  |  |  |

|    |           | 13.2.1         | Creating an SPI slave instance          |  |  |  |

|    |           | 13.2.2         | The SPI slave interface API             |  |  |  |

|    |           |                |                                         |  |  |  |

# 1 Introduction

SPI is a four-wire hardware bi-directional serial interface. This library provides a software defined, industry-standard, SPI (serial peripheral interface) component that allows you to control an SPI bus via the **xcore** GPIO ports.

The SPI bus can be used by multiple tasks within the **xcore** device and (each addressing the same or different slaves) and is compatible with other slave devices on the same bus.

# 2 Available SPI components

Three components are provided in this library which offer different functionality. They are all defined as a task with an interface which provides methods for transmitting and receiving data. All components offer a <code>shutdown()</code> method allowing the component to be exited at runtime which frees any resources used.

#### 2.1 SPI Master (Synchronous)

This component is the standard SPI master and is simplest to use. The *synchronous* aspect refers to the API and operation and means that calls to this component block until the transaction has completed. The component server may be placed on the same or a different tile from the client. If placed on the same tile, the task may be *distributed* by the compiler which means it gets turned into a function call and consequently does not consume an **xcore** thread.

Multiple clients are supported and are arbitrated by the component. Multiple devices are also supported by means of individual slave select bits within a port.

#### 2.2 SPI Master (Asynchronous)

This component offers buffering functionality over the *synchronous* SPI master. The *asynchronous* feature means that calls to this component can be non-blocking and SPI transfers may be queued. The component server may be placed on the same or a different tile from the client.

Due to the buffering logic, the asynchronous version always consumes an xcore thread.

Multiple clients are supported and are arbitrated by the component. Multiple devices are also supported by means of individual slave select bits within a port.

#### 2.3 SPI Slave

The SPI slave component task always runs in its own **xcore** thread because it needs to be responsive to the external master requests. It offers a single slave device with basic 8 or 32 bit transfer support. It provides callbacks for when the slave needs data to transmit or has received data, as well as a callback to indicate the end of a transaction.

#### 3 SPI Modes

The data sample points for SPI are defined by the clock polarity (CPOL) and clock phase (CPHA) parameters. SPI clock polarity may be inverted or non-inverted by the CPOL and the CPHA parameter is used to shift the sampling phase. The following four sections illustrate the MISO and MOSI data lines relative to the clock. The timings are given by:

Table 1: SPI timings

| Parame-<br>ter       | Description                                                                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| t1                   | The minimum time from the start of the transaction (SS asserted) to the first sample point/active clock edge.                                 |

| t2                   | The minimum amount of time from the last sample point/active clock before SS is de-asserted.                                                  |

| t3                   | The inter-transmission gap. This is the minimum amount of time that the slave select must be de-asserted between accesses on the same device. |

| MAX<br>CLOCK<br>RATE | This is the maximum clock rate supported by the configuration.                                                                                |

The setup and hold timings are inherited from the underlying **xcore** device. For details on these timing please refer to the device datasheet.

When operating above 20 Mbps please also see the MISO port timing section.

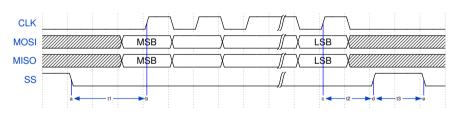

#### 3.1 Mode 0 - CPOL: 0 CPHA 0

Fig. 1: Mode 0

The master and slave will drive out their first data bit before the first rising edge of the clock then drive on subsequent falling edges. They will sample on rising edges.

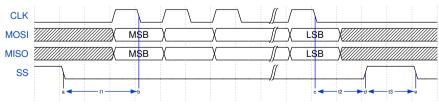

#### 3.2 Mode 1 - CPOL: 0 CPHA 1

Fig. 2: Mode 1

The master and slave will drive out their first data bit on the first rising edge of the clock and sample on the subsequent falling edge.

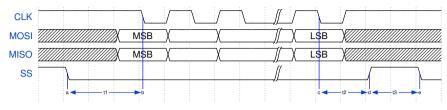

#### 3.3 Mode 2 - CPOL: 1 CPHA 0

Fig. 3: Mode 2

The master and slave will drive out their first data bit before the first falling edge of the clock then drive on subsequent rising edges. They will sample on falling edges.

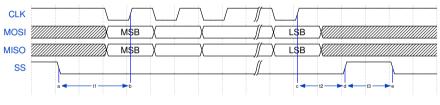

#### 3.4 Mode 3 - CPOL: 1 CPHA 1

Fig. 4: Mode 3

The master and slave will drive out their first data bit on the first falling edge of the clock and sample on the subsequent rising edge.

# 4 External signal description

The SPI protocol requires a clock, one or more slave selects and either one or two data wires.

Table 2: SPI data wires

| Signal                     | Description                                                                                                                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK<br>MOSI<br>MISO<br>SS | Clock line, driven by the master Master Output, Slave Input data line, driven by the master Master Input, Slave Output data line, driven by the slave Slave select line, driven by the master |

During any transfer of data, the master will assert the SS line and then output a series of transitions on the SCLK wire. During this time, the slave will drive data to be sampled by the master and the master will drive data to be sampled by the slave. At the end of the transfer, the SS is de-asserted.

If the slave select line is not driven high then the slave should ignore any transitions on the other lines.

# 5 Connecting to the xcore SPI master

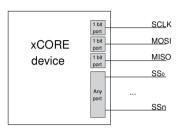

The SPI wires need to be connected to the **xcore** device as shown in Fig. 5. The signals can be connected to any one bit ports, with the exception of slave select which may be any width port. All ports must be on the same tile.

Fig. 5: SPI master connection to the xcore device

If only one data direction is required then the *MOSI* or *MISO* line need not be connected. However, **asynchronous mode is only supported if the MISO line is connected**.

The master component of this library supports multiple slaves on unique slave select wires. The bit of the port used for each device is configurable and so multiple slaves may share the same select bit if needed.

#### 5.1 Disabling master data lines

The MOSI and MISO parameters of the spi\_master() task are optional. So in the top-level par statement the function can be called with null instead of a port e.g.

```

spi_master(i_spi, 1, p_sclk, null, p_miso , p_ss, 1, clk_spi);

```

Similarly, the *MOSI* parameter of the **spi\_master\_async()** task is optional (but the *MISO* port must be provided).

# 6 Connecting to the xcore SPI slave

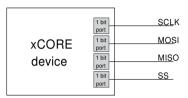

The SPI wires need to be connected to the **xcore** device as shown in Fig. 6. The signals can be connected to any one bit ports on the device.

Fig. 6: SPI slave connection to the xcore device

The slave will only send and receive data when the slave select is driven high. Additionally the MISO line is set to high impedance when not in use.

If the MISO line is not required then it need not be connected. The MOSI line must always be connected.

#### 6.1 Disabling slave data lines

The spi\_slave() task has an optional MISO parameter (but the MOSI port must be supplied).

# 7 Master Usage

#### 7.1 SPI master synchronous operation

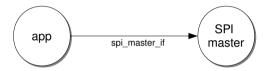

There are two types of interface for SPI master components: synchronous and asynchronous.

The synchronous API provides blocking operation. Whenever a client makes a read or write call the operation will complete before the client can move on - this will occupy the core that the client code is running on until the end of the operation. This method is easy to use, has low resource use and is very suitable for applications such as setup and configuration of attached peripherals.

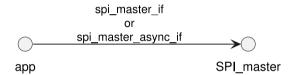

SPI master components are instantiated as parallel tasks that run in a **par** statement. For synchronous operation, the application can connect via an interface connection using the **spi\_master\_if** interface type:

Fig. 7: SPI master task diagram

For example, the following code instantiates an SPI master component and connect to it.

#### Note

The connection is an array of interfaces, so several tasks can connect to the same component instance. The slave select ports are also an array since the same SPI data lines can connect to several devices via different slave lines.

The final parameter of the spi\_master() task is an optional clock block. If the clock block is supplied then the maximum transfer rate of the SPI bus is increased (see Table 3). If null is supplied instead then the performance is lower but no clock block is used.

The application can use the client end of the interface connection to perform SPI bus operations e.g.

```

void my_application(client spi_master_if spi) {

uint8_t val;

printf("Doing one byte transfer. Sending 0x22.\n");

spi.begin_transaction(0, 100, SPI_MODE_0);

val = spi.transfer8(0x22);

spi.end_transaction(1000);

printf("Read data %d from the bus.\n", val);

}

```

Here, <code>begin\_transaction</code> selects the device <code>0</code> and asserts its slave select line. The application can then transfer data to and from the slave device and finish with <code>end\_transaction</code>, which de-asserts the slave select line.

Operations such as <code>spi.transfer8</code> will block until the operation is completed on the bus. More information on interfaces and tasks can be be found in the <code>XMOS</code> Programming Guide. By default the SPI synchronous master mode component does not use any <code>xcore</code> threads of its own. It is a <code>distributed</code> task which means it will perform its function on the <code>xcore</code> thread of the application task connected to it (provided the application task is on the same tile).

#### 7.1.1 Synchronous master usage state machine

The function calls made on the SPI master interface must follow the sequence shown by the state machine in Fig. 8. If this sequence is not followed then the behaviour is undefined.

# shutdown shutdown shutdown shutdown shutdown shutdown

Fig. 8: SPI master use state machine (synchronous)

#### 7.2 SPI master asynchronous operation

The synchronous API will block your application until the bus operation is complete. In cases where the application cannot afford to wait for this long, the asynchronous API can be used.

The asynchronous API offloads operations to another task. Calls are provided to initiate reads and writes and notifications are provided when the operation completes. This API requires more management in the application but can provide much more efficient operation.

It is particularly suitable for applications where the SPI bus is being used for continuous data transfer.

Setting up an asynchronous SPI master component is done in the same manner as the synchronous component.

The application can use the asynchronous API to offload bus operations to the component. This is done by moving pointers to the SPI slave task to transfer and then retrieving pointers when the operation is complete. For example, the following code repeatedly calculates 100 bytes to send over the bus and handles 100 bytes coming back from the slave.

The SPI asynchronous task is combinable so can be run on a logical core with other tasks (including the application task it is connected to).

#### 7.2.1 Asynchronous master command buffering

In order to provide asynchronous behaviour for multiple clients the asynchronous master will store up to one <code>begin\_transaction</code> and one <code>init\_transfer\_array\_8</code> or <code>init\_transfer\_array\_32</code> from each client. This means that if the master is busy doing a transfer for client *X*, then client *Y* will still be able to begin a transaction and send data fully asynchronously. Consequently, after client *Y* has issued <code>init\_transfer\_array\_8</code> or <code>init\_transfer\_array\_32</code> it will be able to continue operation whilst waiting for the notification.

#### 7.2.2 Asynchronous master usage state machine

The function calls made on the SPI master asynchronous interface must follow the sequence shown by the state machine in Fig. 9. If this sequence is not followed then the behaviour is undefined.

# SPI master use state machine (asynchronous) begin\_transaction init\_transfer\_array\_8 init transfer array 32 transfer\_complete retrieve\_transfer\_buffers 8 retrieve transfer buffers 32 end transaction shutdown

Fig. 9: SPI master use state machine (asynchronous)

# 7.3 Master inter-transaction gap

For both synchronous and asynchronous modes the <code>end\_transaction</code> requires a slave select de-assert time. This parameter will provide a minimum de-assert time between two transaction on the same slave select. In the case where a <code>begin\_transaction</code> asserting the slave select would violate the previous <code>end\_transaction</code> then the <code>begin\_transaction</code> will block until the slave select deassert time has been satisfied.

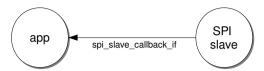

# 8 Slave usage

SPI slave components are instantiated as parallel tasks that run in a par statement. The application can connect via an interface connection.

Fig. 10: SPI slave task diagram

For example, the following code instantiates an SPI slave component and connect to it.

When a slave component is instantiated the mode and transfer size needs to be specified. If you wish to change mode or width, you can shutdown the component and re-start it.

The slave component acts as the client of the interface connection. This means it can "callback" to the application to respond to requests from the bus master. For example, the following code snippet shows part of an application that responds to SPI transactions where the first word is a command to read or write command and subsequent transfers either provide or consume data.

```

while (1) {

uint32_t command = 0;

size_t index = 0;

select {

case spi master_requires_data() -> uint32_t data:

if (command == 0) {

// Not got the command yet. This will be the

// first word of the transaction.

data = 0;

} else if (command == READ_COMMAND) {

data = get_read_data_item(index);

index+++;

} else {

data = 0;

}

break;

case spi.master_supplied_data(uint32_t data, uint32_t valid_bits):

if (command == 0) {

command = data;

} else if (command == WRITE_COMMAND) {

handle_write_data_item(data, index);

index++;

}

break;

case spi.master_ends_transaction():

// The master has de-asserted slave select.

command = 0;

index = 0;

break;

}

}

```

#### Note

The time taken to handle the callbacks will determine the timing requirements of the SPI slave and so should be kept as short as possible. See the SPI slave example in <code>examples/app\_spi\_slave</code> for more details on different ways of working with the SPI slave component.

# 9 SPI master timing characteristics

#### 9.1 Synchronous SPI master clock speeds

The maximum speed that the SPI bus can be driven depends on whether a clock block is used, the speed of the **xcore** thread that the SPI code is running on and where both the *MISO* and *MOSI* lines are used. The timings can be seen in Table 3.

Table 3: SPI master timings (synchronous)

| Clock<br>blocks | MOSI en-<br>abled | MISO en-<br>abled | Max kbps (62.5 MHz core) | Max kbps (100 MHz<br>core) |

|-----------------|-------------------|-------------------|--------------------------|----------------------------|

| 0               | 1                 | 0                 | 2500                     | 3500                       |

| 0               | 1                 | 1                 | 1200                     | 1300                       |

| 1               | 1                 | 0                 | 62500                    | 75000                      |

| 1               | 1                 | 1                 | 62500                    | 75000                      |

#### 9.2 Asynchronous SPI master clock speeds

The asynchronous SPI master uses the same transport layer as the SPI master using a clock block and so achieves similar performance.

Table 4: SPI master timings (asynchronous)

| Clock<br>blocks | MISO en-<br>abled | MOSI en-<br>abled | Max kbps (62.5 MHz core) | Max kbps (100 MHz core) |

|-----------------|-------------------|-------------------|--------------------------|-------------------------|

| 1               | Χ                 | X                 | 62500                    | 75000                   |

#### 9.3 MISO port timing

Port timing is affected by chip pad and PCB delays. For the clock, slave-select and MOSI signals, all of the delays will be broadly matched. This means port timing adjustment is normally not required even up to the fastest supported SPI clock rates.

For the MISO signal, there will be a 'round trip delay' starting with the clock edge output and finishing at the **xcore**'s input port. The presence of this delay will mean the **xcore** may sample too early since data signal will arrive later. It may be necessary to delay the sampling of the MISO pin to capture within the required window, particularly if the SPI clock is above 20 MHz.

Control over the signal capture is provided for all SPI master implementations that require a clock block. Please see the *API section spi\_master\_sync\_timings()* method which exposes the controls available for optimising setup and hold capture.

For details on how to calculate and adjust round-trip port timing, please consult the IO timings for xcore.ai or IO timings for xCORE200 document.

# 10 SPI slave timing characteristics

The **xcore** thread running the SPI slave task will wait for the slave select line to assert and then begin processing the transaction. At this point it will call the **master\_requires\_data** callback to application code. The time taken for the application to perform this call will affect how long the **xcore** thread has to resume processing SPI data. This will affect the minimum allowable time between slave select changing and data transfer from the master (t1).

The user of the library will need to determine this time based on their application.

After slave select is de-asserted the SPI slave task will call the **master\_ends\_transaction** callback. The time the application takes to process this will affect the minimum allowable inter-transmission gap between transactions (*t2*). The user of the library will also need to determine this time based on their application.

If the SPI slave task is combined will other tasks running on the same **xcore** thread then the other task may process an event delaying the time it takes for the SPI slave task to react to events. This will add these delays to the minimum times for both *t1* and *t2*. The library user will need to take these into account in determining the timing restrictions on the master.

#### Note

The time taken to handle the callbacks will determine the timing requirements of the SPI slave, and so must be kept as short as possible.

Throughput for SPI slave versus mode and MOSI usage is shown in the following table.

SPI Mode MOSI enabled Max kbps (62.5 MHz core) Max kbps (100 MHz core)

Table 5: SPI slave timings

# 11 Examples

#### 11.1 SPI Master Example

#### 11.1.1 Overview

The example uses the XMOS SPI library to perform some bus transactions as SPI master. The SPI master examples are run on the *xcore.ai* evaluation kit, XK-EVK-XU316 using the WFM200 WiFi device as a simple SPI slave.

The application consists of two tasks:

- A task that drives the SPI bus

- ► An application task that connects to the SPI task

These tasks communicate via the use of xC interfaces. Note that for the SPI synchronous cases, even though the SPI master and app are separate tasks, the compiler is able to distribute the SPI master so that the application only uses a single hardware thread.

Fig. 11 shows the task and communication structure of the application.

Fig. 11: Task diagram of SPI master example

#### 11.1.2 Declaring ports

The SPI library connects to external pins via **xcore** ports. In **main.xc** these are declared as variables of type **port** at the start of the file:

#### Note

The slave select declaration is for a mulit-bit port. The pin in this port that will be used as SPI SS set by spi.set\_ss\_port\_bit(0, 1);

How the ports (e.g. XS1\_PORT\_1I) relate to external pins will depend on the exact device being used. See the device datasheet for details.

#### 11.1.3 The application main() function

Below is the source code for the main function of this application, which is taken from the source file main.xc

```

int main(void) {

interface spi_master_async_if i_spi_async[1];

par {

on tile[0]: {

par {

async_app(i_spi_async[0]);

spi_master_async(i_spi_async, 1, p_sclk, p_mosi, p_miso, p_ss, 1, clk);

}

}

return 0;

}

int main(void) {

interface spi_master_if i_spi[1];

par {

on tile[0]: app(i_spi[0]);

on tile[0]: spi_master(i_spi, 1, p_sclk, p_mosi, p_miso, p_ss, 1, CLKBLK);

}

return 0;

}

```

Looking at this in more detail you can see the following:

- ▶ The par functionality describes running two separate tasks in parallel

- ► The spi\_master() or spi\_master\_async() task drives the SPI bus and takes the ports it will use as arguments.

- ▶ The app() or app\_async() task communicates to the SPI master task via the shared interface argument i\_spi or i\_spi\_async. This is an array since the SPI master task could connect to many other tasks (clients) in parallel.

#### 11.1.4 The app() task

The app() task uses its interface connection to the SPI master task to perform SPI transactions. It performs two transactions (each transaction will assert the slave select line, transfer some data and then de-assert the slave select line). The functions in the SPI master interface can be found in the SPI library user guide.

```

void app(client spi_master_if spi)

uint8 t val:

printstrln("Sending SPI traffic");

p_rstn <: RESET_DEASSERT; //Take out of reset and wait

delay_microseconds(POST_RESET_DELAY_MICROSECONDS);

spi.set_ss_port_bit(0, 1); // We are using bit 1 in WIFI_CS_N for device \theta

spi.begin_transaction(0, SPI_SPEED_KBPS, SPI_MODE_0);

uint32_t reg_addr = 0; // Read reg 0 CONFIG register

uint32_t read_cmd = 0x8000;

uint32_t num_16b_words = 2;

uint32_t reg_addr_shift = 12;

uint32_t command = read_cmd | num_16b_words | (reg_addr << reg_addr_shift); //Do read command</pre>

val = spi.transfer8(command >> 8);// MSB first

val = spi.transfer8(command & 0xff);

uint32_t req;

reg = spi.transfer32(0x00); //Read result

spi.end_transaction(0);

printhexln(reg >> 16); // Should be 0x5400

printstrln("Done.");

spi.shutdown();

```

(continued from previous page)

```

p_rstn <: RESET_DEASSERT; //Take out of reset and wait

delay_microseconds(POST_RESET_DELAY_MICROSECONDS);</pre>

spi.set_ss_port_bit(0, 1); // We are using bit 1 in WIFI_CS_N for device 0

spi.begin_transaction(0, SPI_SPEED_KBPS, SPI_MODE_0);

uint32_t reg_addr = 0; // Read reg 0 CONFIG register

uint32_t read_cmd = 0x8000;

uint32_t num_16b_words = 2;

uint32_t reg_addr_shift = 12;

uint32_t command = read_cmd | num_16b_words | (reg_addr << reg_addr_shift); //Do read command</pre>

uint8_t outbuffer[2];

outbuffer[0] = (command >> 8) & 0xff; // MSB first outbuffer[1] = command & 0xff;

\begin{subarray}{lll} \textbf{uint8}\_\textbf{t} * movable inbuf = NULL; // We do not care about the read data for the cmd write $\begin{subarray}{lll} \textbf{uint8}\_\textbf{t} * movable outbuffer; \end{subarray}

// This call passes the buffers over to the SPI task, after // this the application cannot access the buffers until

// the retrieve_transfer_buffers_8 function is called.

spi.init_transfer_array_8(move(inbuf)

move(outbuf).

// A select will wait for an event. In this case the event we are waiting // for is the transfer_complete() notification event from the SPI task.

select {

case spi.transfer complete():

// Once the transfer is complete, we can retrieve the // buffers back into the inbuf and outbuf pointer variables

spi.retrieve_transfer_buffers_8(inbuf, outbuf);

spi.begin_transaction(0, SPI_SPEED_KBPS, SPI_MODE_0);

uint32_t inbuffer32[1] = {0};

uint32_t * movable inbuf32 = inbuffer32;

uint32_t * movable outbuf32 = NULL; // We do not care what is written during reg reads

spi.init_transfer_array_32(move(inbuf32),

null,

1);

case spi.transfer_complete():

// Once the transfer is complete, we can retrieve the

// buffers back into the inbuf and outbuf pointer variables

spi.retrieve_transfer_buffers_32(inbuf32,

outbuf32):

break;

printhexln(*inbuf32 >> 16); // Should be 0x5400

printstrln("Done.");

spi.shutdown();

```

#### Note

When **begin\_transaction** is called the SPI device selected is determined by the first argument. In this case it is **0**. This is the method that is used to communiate with multiple SPI slave devices. The speed and mode of the SPI protocol is also set at in the **begin\_transaction** call.

#### 11.1.5 Building

The following section assumes that the XMOS XTC tools has been downloaded and installed (see *README* for required version).

Installation instructions can be found here. Particular attention should be paid to the section Installation of required third-party tools.

The application uses the *XMOS* build and dependency system, xcommon-cmake. xcommon-cmake is bundled with the *XMOS* XTC tools. It runs on the xcore.ai evaluation kit, XK-EVK-XU316.

To configure the build, run the following from an XTC command prompt:

```

cd examples

cd app_spi_master

cmake -G "Unix Makefiles" -B build

```

Any missing dependencies will be downloaded by the build system at this configure step.

Finally, the application binaries can be built using xmake:

```

xmake -j -C build

```

Multiple build profiles are included and will be built as follows:

- ▶ ASYNC Example of using the asynchronous SPI master

- SYNC Example of using the synchronous SPI master with clock-block (high performance)

- SYNC\_NO\_CLKBLK Example of using the synchronous SPI master without clockblock (low performance / low resource usage)

The build profiles are guarded by the defines *SPI\_USE\_ASYNC=1* for specifying the asynchronous SPI master and *CLKBLK=null* when using the synchronous SPI master which determines which underlying SPI master transport to use.

#### 11.1.6 **Running**

To run the application return to the <code>/examples/app\_spi\_master</code> directory and run the following command:

```

xrun --xscope bin/SYNC/app_spi_master_SYNC.xe

```

As application runs that reads a value from the SPI connected WiFi chip and prints the following output to the console:

```

Sending SPI traffic 5400 Done.

```

The value 5400 represents bits 15 to 0 of the default value of the CONFIG register of the WFM200.

Likewise, the following two commands should yield the same console output:

```

xrun --xscope bin/SYNC/app_spi_master_SYNC_NO_CLKBLK.xe

xrun --xscope bin/SYNC/app_spi_master_ASYNC.xe

```

#### 11.2 SPI Slave Example

#### 11.2.1 Overview

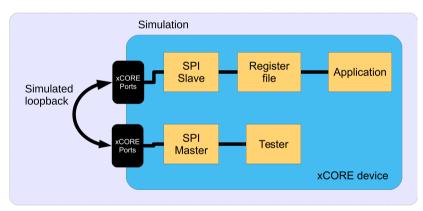

The example in this application note uses the XMOS SPI library to act as SPI slave. It maintains a register file which can be read and written by the internal application *or* by the master on the SPI bus. To show the bus functioning the demo application also has a tester component connected to an SPI master bus which is connected (in simulation) to the the SPI slave, using the simulator loopback plug-in. This allows generation of SPI traffic to show the communication functioning.

The application consists of five tasks:

- ▶ A task that controls the SPI slave ports

- ▶ A task that implements the register file handling calls from the SPI slave component and the application

- ▶ An application task that connects to the register file task

- ▶ A task that controls the SPI master ports used for testing

- A tester task that outputs commands to the SPI master task

Fig. 12 shows the task and communication structure of the application.

Fig. 12: Block diagram of SPI slave application example

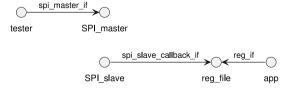

These tasks communicate via the use of xC interfaces. Fig. 13 shows the task and communication structure of the application.

Fig. 13: Task diagram of SPI slave example

#### 11.2.2 Declaring ports

The SPI library connects to external pins via **xcore** ports. In **main.xc** these are declared as variables of type **port** at the start of the file:

#### 6 Note

There is also a clock declaration since the slave needs to use an internal clock as well as ports inside the **xcore** device.

How the ports (e.g. XS1\_PORT\_1I) relate to external pins will depend on the exact device being used. See the device datasheet for details.

This application also has an SPI master interface on different ports:

#### 11.2.3 The application main() function

Below is the source code for the main function of this application, which is taken from the source file main.xc

Looking at this in a more detail you can see the following:

- ▶ The par functionality describes running five separate tasks in parallel; three are for the main application and two are for the tester.

- ▶ The spi\_slave() task controls the application SPI bus and takes the ports it will use as arguments.

- ▶ The reg\_file() task is connected to the app() task and the spi\_slave() task.

- ▶ The spi\_slave() task has an argument for the mode it expects in this case Mode 0 (see the SPI library user guide for more details on modes)

- ► The spi\_slave() task also has an argument SPI\_TRANSFER\_SIZE\_8 which specifies the size of data chunk it will use when making callbacks to the application.

- ▶ The spi\_master() task controls the test SPI bus and takes different ports to the SPI slave bus as arguments. For details on using SPI master see application note AN00160.

#### 11.2.4 The reg\_file() task

The **reg\_file()** task is the main logic of this example. It will respond to calls from the application and the SPI slave bus whilst maintaining a set of register values.

The task is marked as [[distributable]] which means it can only responds to calls from other tasks, rather than resource events. The main reason for this is so that the reg\_file() task itself does not need a hardware thread of its own it can use the hardware thread of the task that calls it. See the XMOS programming guide for details of distributable tasks.

The function takes two arguments, the interface connections to the application task and the SPI slave task:

The reg\_if interface has been defined in main.xc earlier. It defines the functions that the app may call in the reg\_file() tasks:

```

typedef interface reg_if {

uint8_t get_reg(uint8_t regnum);

void set_reg(uint8_t regnum, uint8_t value);

} reg_if;

```

In this case we have two functions - one for reading a register value and one for writing a register value.

The reg\_file() task first declares its state - an array to hold register value, a state variable to hold what stage of an SPI transaction it is in and the currently addressed register by the SPI bus.

```

/* This array holds the register values */

uint8_t reg_data[NUM_REG] = {0};

/* This variable holds the current state of the register file with respect

* to the SPI bus (i.e. what stage of the transaction over SPI it is at).

*/

enum reg_state_t state = IDLE;

/* This variable holds the current register being addressed over the SPI

* bus.

*/

uint8_t addr = 0;

```

The state variable is just an integer from the following **enum** type defined earlier in the file:

```

enum reg_state_t {

WRITE_REG = 0,

READ_REG = 1,

WRITE_REG_DATA,

READ_REG_DATA,

IDLE

};

```

The implemented protocol on the SPI bus is as follows:

- ▶ The master will start a transaction (assert slave select)

- ▶ It will then send a byte of either a 0 for a write or a 1 for a read.

- ▶ It will then send the address of the register to read/write

- ▶ It will then send or receive the value of the register

To implement the protocol logic the <code>reg\_file()</code> task must continually react to events from the SPI slave tasks keeping track of its state, updating registers and supplying the correct outputs. This is done via a <code>while(1)</code> loop with an xC <code>select</code> statement inside it. A <code>select</code> statement will wait and then react to various events or calls from different tasks - see the XMOS programming guide for more details.

The following cases in the main loop of the function handle this:

```

/* These cases react to the SPI slave bus. A write from the bus will

* update the state of the transaction. A read from the bus will get

* sent the data from the currently addressed register. */

case i spi.master ends transaction(void):

state = IDLE;

break:

case i_spi.master_requires_data(void) -> uint32_t data:

data = reg_data[addr];

break;

e i_spi_master_supplied_data(uint32_t datum, uint32_t valid_bits):

case i

switch (state) {

if (datum == WRITE_REG || datum == READ_REG)

state = datum:

break;

case READ_REG:

if (datum < NUM_REG) {

addr = datum;

state = READ_REG_DATA;

} else {

state = IDLE;

break;

case READ_REG_DATA:

// Do nothing with master data during a read data operation.

break;

case WRITE_REG:

if (datum < NUM_REG) {</pre>

addr = datum;

state = WRITE_REG_DATA;

} else {

state = IDLE;

break;

case WRITE_REG_DATA:

reg_data[addr] = datum;

break:

break:

```

We can see that the slave will always send the value of the currently addressed register on every data transfer (this is allowable in the described protocol).

When the SPI master supplies some data to the slave then what happens depends on the current state - either the state variable is updated, the currently addressed register is updated or a register value is updated. This state machine will implement the previously described protocol.

The main **select** statement also needs to react to request from the application. The following cases implement this:

```

/* The following cases respond to the application when it

* requests to get/set a register.

*/

case i_reg.get_reg(uint8_t regnum) -> uint8_t value:

value = reg_data[regnum];

break;

case i_reg.set_reg(uint8_t regnum, uint8_t value):

reg_data[regnum] = value;

break;

```

#### 11.2.5 The app() task

The app() task represents a sample application task that uses the register file. In this demo, it doesn't do much - it simple sets one register and repeatedly polls the value of another register and prints out its value:

#### Note

The **debug\_printf** function comes from the **debug\_print.h** header supplied by **lib\_logging**. It is a low memory debug printing function that will print out messages to the console (either using JTAG or xSCOPE to communicate to the host via the debug adaptor).

#### 11.2.6 The tester() task

The tester task will send some test data to the SPI master bus. It does this using the SPI master interface to communicate with the SPI master task:

```

void tester(client spi_master_if spi)

{

delay_microseconds(50); // Wait for slave to init

uint8_t val;

spi.begin_transaction(0, SPI_SPEED_KBPS, SPI_MODE_0);

spi.transfer8(READ_REG); // READ command

spi.transfer8(0); // READ command

spi.transfer8(0); // DATA

spi.end_transaction(SPI_SS_DELAY_10NS_TICKS);

debug_printf("SPI_MASTER: Read register 0: 0%%x\n", val);

spi.begin_transaction(0, SPI_SPEED_KBPS, SPI_MODE_0);

spi.transfer8(NRITE_REG); // WRITE command

spi.transfer8(1); // REGISTER 1

spi.transfer8(0); // DATA

spi.end_transaction(SPI_SS_DELAY_10NS_TICKS);

printstr("SPI_MASTER: Set register 1 to 0xAc\n");

delay_microseconds(100);

_Exit(0);

}

```

#### 11.2.7 Building

The following section assumes that the XMOS XTC tools has been downloaded and installed (see *README* for required version).

Installation instructions can be found here. Particular attention should be paid to the section Installation of required third-party tools.

The application uses the *XMOS* build and dependency system, xcommon-cmake. xcommon-cmake is bundled with the *XMOS* XTC tools. It runs on the xcore.ai evaluation kit, XK-EVK-XU316.

To configure the build, run the following from an XTC command prompt:

```

cd examples

cd app_spi_slave

cmake -G "Unix Makefiles" -B build

```

Any missing dependencies will be downloaded by the build system at this configure step.

Finally, the application binaries can be built using **xmake**:

```

xmake -j -C build

```

#### **11.2.8 Running**

To run the application return to the **/examples/app\_spi\_slave** directory and run the following command:

```

xsim --xscope '-offline trace.xmt' bin/app_spi_slave.xe \

--trace-plugin VcdPlugin.dll '-tile tile[0] -o trace.vcd -xe bin/app_spi_slave.xe \

-ports -functions -cores -instructions' --plugin LoopbackPort.dll \

'-port tile[0] XSI_PORT_II 1 0 -port tile[0] XSI_PORT_IE 1 0 \

-port tile[0] XSI_PORT_II 1 0 -port tile[0] XSI_PORT_IE 1 0 \

-port tile[0] XSI_PORT_IK 1 0 -port tile[0] XSI_PORT_IE 1 0 \

-port tile[0] XSI_PORT_IK 1 0 -port tile[0] XSI_PORT_IE 1 0 \

-port tile[0] XSI_PORT_IL 1 0 -port tile[0] XSI_PORT_IE 1 0 \

```

#### Note

This command line is provided as a file in the <code>/examples/app\_spi\_slave</code> directory under the filename <code>simulate\_cmd.txt</code>. You can rename this file to <code>simulate\_cmd.sh</code> or <code>simulate\_cmd.bat</code> and run it directly, depending on your host OS.

As application runs that reads a value from the SPI connected WiFi chip and prints the following output to the console:

```

APP: Set register 0 to 0xED

APP: Register 0 is 0xED, Register 1 is 0x0

APP: Register 0 is 0xED, Register 1 is 0x0

APP: Register 0 is 0xED, Register 1 is 0x0

SPI MASTER: Read register 0: 0xED

APP: Register 0 is 0xED, Register 1 is 0x0

SPI MASTER: Set register 1 to 0xAC

APP: Register 0 is 0xED, Register 1 is 0xAC

APP: Register 0 is 0xED, Register 1 is 0xAC

APP: Register 0 is 0xED, Register 1 is 0xAC

```

Both registers were initialised to 0x00 so you can see the successful application side write to register 0 of value 0xED, followed by the SPI master read of that register shortly afterwards. You can also see that the SPI master writes to register 1 with the value of 0xAC which is then successfully read by the application.

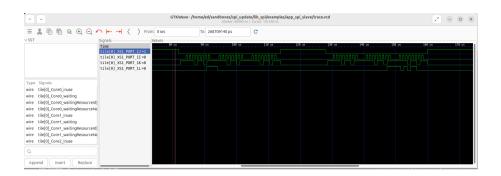

If you wish, you can also view the simulation in a VCD (Voltage Change Description) viewer, such as **gtkwave**, by running the following command:

```

gtkwave slave_simulation.gtkw

```

This will show the four SPI lines and zoom into the section where the SPI transactions occur, as can be seen in Fig. 14.

Fig. 14: VCD waveform trace for SPI slave with registers simulation

# 12 Resource Usage

Each of the SPI implementations use a number of *xcore* resources which include ports, clock-blocks and may include hardware threads. The table Table 6

Table 6: xcore resource usage for SPI

| configuration                           | арі                                                                               | pins | ports                     | thread |

|-----------------------------------------|-----------------------------------------------------------------------------------|------|---------------------------|--------|

| Master (synchronous, zero clock blocks) | spi_master(i, 1, p_sclk, p_mosi, p_miso, p_ss, 1, null);                          | 4    | 3 * 1-bit, 1<br>* any-bit | 0      |

| Master (synchronous, one clock block)   | spi_master(i, 1, p_sclk, p_mosi, p_miso, p_ss, 1, cb);                            | 4    | 3 * 1-bit, 1<br>* any-bit | 0      |

| Master (asyn-<br>chronous)              | spi_master_async(i, 1, p_sclk, p_mosi, p_miso, p_ss, 1, cb);                      | 4    | 3 * 1-bit, 1<br>* any-bit | 1      |

| Slave (32 bit transfer mode)            | spi_slave(i, p_sclk, p_mosi, p_miso, p_ss, cb, SPI_MODE_0, SPI_TRANSFER_SIZE_32); | 4    | 4 (1-bit)                 | 1      |

| Slave (8 bit transfer mode)             | spi_slave(i, p_sclk, p_mosi, p_miso, p_ss, cb, SPI_MODE_0, SPI_TRANSFER_SIZE_8);  | 4    | 4 (1-bit)                 | 1      |

The number of pins is reduced if either of the data lines are not required.

#### 13 API Reference

#### 13.1 Master API

All SPI master functions can be accessed via the spi.h header:

```

#include "spi.h"

```

You will also have to add **lib\_spi** to the application's **APP\_DEPENDENT\_MODULES** list in *CMakeLists.txt*, for example:

```

set(APP_DEPENDENT_MODULES "lib_spi")

```

#### 13.1.1 Supporting types

The following type is used to configure the SPI components.

#### enum spi\_mode\_t

This type indicates what clocking mode a SPI component should use *Values*:

```

enumerator SPI_MODE_0

SPI Mode 0 - Polarity = 0, Phase = 0

enumerator SPI_MODE_1

SPI Mode 1 - Polarity = 0, Phase = 1

enumerator SPI_MODE_2

SPI Mode 2 - Polarity = 1, Phase = 0

enumerator SPI_MODE_3

SPI Mode 3 - Polarity = 1, Phase = 1

```

#### struct spi\_master\_ss\_clock\_timing\_t

This type contains timing settings for SS assert to clock delay and last clock to SS de-assert delay. The unit is reference timer ticks which is nominally 10 ns. The maximum setting is 65535 which equates to 655 us, over which the setting will overflow back to zero

#### struct spi\_master\_miso\_capture\_timing\_t

This type contains timing settings for capturing the MISO pin for SPI master. When the SPI clock is above 20MHz it is usually necessary to delay the sampling of the MISO pin. These settings can be coarse grained using miso\_sample\_delay setting which increments in SPI half clocks or fine grained in units of core clock (eg. 600 MHz -> 1.66 ns) using the miso\_pad\_delay setting.

See the following document for details on xcore.ai port timing: https://www.xmos.com/documentation/XM-014231-AN/html/rst/index.html

#### 13.1.2 Creating an SPI master instance

#### void spi\_master(

)

$\label{eq:server_inter} SERVER_INTERFACE (spi\_master\_if, i[num\_clients]), static\_const\_size\_t \\ num\_clients, out\_buffered\_port\_32\_t sclk, NULLABLE\_RESOURCE (out\_buffered\_port\_32\_t, mosi), NULLABLE\_RESOURCE (in\_buffered\_port\_32\_t, miso), out\_port p\_ss, static\_const\_size\_t num\_slaves, NULLABLE\_RESOURCE (clock, clk), \\ \end{aligned}$

Task that implements the SPI proctocol in master mode that is connected to a multiple slaves on the bus.

Each slave must be connected to using the same SPI mode.

You can access different slave devices over the interface connection using the device\_index parameter of the interface functions. The task will allocate the device indices in the order of the supplied array of slave select ports.

#### **Parameters**

- ▶ i An array of interface connection to the clients of the task.

- ▶ num\_clients The number of clients connected to the task.

- ▶ clk a clock block used by the task.

- ▶ sclk The SPI clock port.

- ▶ mosi The SPI MOSI (master out, slave in) port.

- ▶ miso The SPI MISO (master in, slave out) port.

- p\_ss A port connected to the slave select signals of the slave. Multiple slaves may be supported by specifying, for example, a 4-bit port. Please specify mapping of bits to slaves using i.set\_ss\_port\_bit().

- ▶ num\_slaves The number of slave devices on the bus.

- clk A clock for the component to use. May be set to null if low speed operation is acceptable.

#### void spi\_master\_async(

SERVER\_INTERFACE(spi\_master\_async\_if, i[num\_clients]), static\_const\_size\_t num\_clients, out\_buffered\_port\_32\_t sclk, NULLABLE\_RESOURCE(out\_buffered\_port\_32\_t, mosi), in\_buffered\_port\_32\_t miso, out\_port p\_ss, static\_const\_size\_t num\_slaves, clock clk,

SPI master component for asynchronous API.

This component implements SPI and allows a client to connect using the asynchronous SPI master interface.

#### **Parameters**

- ▶ i an array of interface connection to the clients of the task.

- ▶ num\_clients the number of clients connected to the task.

- ▶ sclk the SPI clock port.

- ▶ mosi the SPI MOSI (master out, slave in) port.

- ▶ miso the SPI MISO (master in, slave out) port.

- ▶ p\_ss a port of any width which outputs the slave select signals

- ▶ num\_slaves The number of slave devices on the bus.

- ▶ clk a clock block for the component to use.

)

#### 13.1.3 SPI master interface

#### group Spi\_master\_if

This interface allows clients to interact with SPI master task.

Methods for synchronous SPI master interface.

#### **Functions**

```

void begin_transaction(

unsigned device_index, unsigned speed_in_khz, spi_mode_t mode,

)

```

Begin a transaction.

This will start a transaction on the bus. During a transaction, no other client to the SPI component can send or receive data. If another client is currently using the component then this call will block until the bus is released.

#### **Parameters**

- device\_index The index of the slave device to interact with

- speed\_in\_khz The speed that the SPI bus should run at during the transaction (in kHZ). When using the version with clockblock, the minimum speed is 100 kHz.

- ▶ mode The mode of spi transfers during this transaction.

#### void end\_transaction(unsigned ss\_deassert\_time)

End a transaction.

This ends a transaction on the bus and releases the component to other clients.

#### **Parameters**

ss\_deassert\_time - The minimum time in reference clock ticks between assertions of the selected slave select. This time will be ignored if the next transaction is to a different slave select.

#### uint8\_t transfer8(uint8\_t data)

Transfer a byte over the SPI bus.

This function will transmit and receive 8 bits of data over the SPI bus. The data will be transmitted least-significant bit first.

#### **Parameters**

▶ data - The data to transmit the MOSI port.

#### Returns

The data read in from the MISO port.

```

uint32_t transfer32(uint32_t data)

```

Transfer a 32-bit word over the SPI bus.

This function will transmit and receive 32 bits of data over the SPI bus. The data will be transmitted least-significant bit first and most significant byte first (big endian)

#### **Parameters**

data – The data to transmit the MOSI port.

#### **Returns**

The data read in from the MISO port.

#### void transfer\_array(

)

$\label{eq:nullable_array_of_const} NULLABLE\_ARRAY\_OF(uint8\_t, data\_out) \text{, } NULLABLE\_ARRAY\_OF(uint8\_t, data\_in) \text{, } static\_const\_size\_t num\_bytes \text{,} \\$

Transfer an array of bytes over the SPI interface.

This function will transmit and receive 32 bits of data over the SPI bus. The data will be transmitted least-significant bit first in byte order in memory. Note that XMOS uses little endian and so 32b data etc. may need byteswap() first.

#### **Parameters**

- data\_out Reference to data to transmit the MOSI port. May be null if only a read is needed.

- data\_in Reference to data to receive from the MISO port. May be null if only a write is needed.

- num\_bytes Constant value of the size of the array to be transferred.

#### void set\_ss\_port\_bit(unsigned device\_index, unsigned ss\_port\_bit)

Sets the bit of port which is used for slave select (> 1b port type only) and only for spi\_master. spi\_master sets all bits in each port high/low

The default value (if this is not called) is the bit number is equal to the device\_index (device 0-> bit 0, device 1-> bit 1 etc.).

#### **Parameters**

- device\_index The index of the device for which the port bit is to be set.

- ss\_port\_bit Which bit number in the port to use for slave select

#### void set\_miso\_capture\_timing(

unsigned device\_index, spi\_master\_miso\_capture\_timing\_t miso\_capture\_timing,

Configures the timing parameters for MISO capture. At frequencies above 20 MHz it is likely that some capture delays will need to be introduced to ensure setup and hold times are met. These settings only affect the fast SPI master which uses a clock block.

See the following document for details on xcore.ai port timing: https://www.xmos.com/documentation/XM-014231-AN/html/rst/index.html

#### **Parameters**

- device\_index The index of the device for which the MISO timing is to be set.

- ▶ miso\_capture\_timing A structure of type spi\_master\_miso\_capture\_timing\_t with the desired settings.

#### void set\_ss\_clock\_timing(

unsigned device\_index, spi\_master\_ss\_clock\_timing\_t ss\_clock\_timing,

Configures the timing settings for SS assert to clock delay, and last clock to SS de-assert delay. The unit is reference timer ticks which is nominally 10 ns. The maximum setting is 65535 which equates to 655 us over which the setting will overflow back to zero. These settings only affect the fast SPI master which uses a clock block.

#### **Parameters**

- device\_index The index of the device for which the SS timing is to be set.

- ► ss\_clock\_timing A structure of type spi\_master\_ss\_clock\_timing\_t with the desired settings.

void shutdown(void)

Shut down the SPI master interface server.

#### 13.1.4 SPI master asynchronous interface

```

group Spi_master_async_if

```

Asynchronous interface to an SPI component.

This interface allows programs to offload SPI bus transfers to another task. An asynchronous notification occurs when the transfer is complete.

Methods for asynchronous SPI master interface.

#### **Functions**

```

void begin_transaction(

unsigned device_index, unsigned speed_in_khz, spi_mode_t mode,

)

```

Begin a transaction.

This will start a transaction on the bus. During a transaction, no other client to the SPI component can send or receive data. If another client is currently using the component then this call will block until the bus is released.

#### **Parameters**

- device\_index The index of the slave device to interact with.

- speed\_in\_khz The speed that the SPI bus should run at during the transaction (in kHZ). The minimum speed is 100 kHz.

- ▶ mode The mode of spi transfers during this transaction

void end\_transaction(unsigned ss\_deassert\_time)

End a transaction.

This ends a transaction on the bus and releases the component to other clients.

#### **Parameters**

▶ ss\_deassert\_time - The minimum time in reference clock ticks between assertions of the selected slave select. This time will be ignored if the next transaction is to a different slave select

```

void init_transfer_array_8(

uint8_t_movable_ptr_t inbuf, uint8_t_movable_ptr_t outbuf, size_t nbytes,

)

```

Initialize Transfer an array of bytes over the SPI bus.

This function will initialize a transmit of 8 bit data over the SPI bus.

#### **Parameters**

- inbuf A movable pointer that is moved to the other task pointing to the buffer area to fill with data. If this parameter is NULL then the incoming data of the transfer will be discarded.

- outbuf A movable pointer that is moved to the other task pointing to the buffer area to with data to transmit. If this parameter is NULL then the outgoing data of the transfer will consist of undefined values.

- ▶ **nbytes** The number of bytes to transfer over the bus.

```

void init_transfer_array_32(

uint32_t_movable_ptr_t inbuf, uint32_t_movable_ptr_t outbuf, size_t nwords,

)

```

in-

Initialize Transfer an array of bytes over the SPI bus.

This function will initialize a transmit of 32 bit data over the SPI bus.

#### **Parameters**

- ▶ inbuf A movable pointer that is moved to the other task pointing to the buffer area to fill with data. If this parameter is NULL then the incoming data of the transfer will be discarded.

- outbuf A movable pointer that is moved to the other task pointing to the buffer area to with data to transmit. If this parameter is NULL then the outgoing data of the transfer will consist of undefined values.

- nwords The number of words to transfer over the bus.

#### void transfer\_complete(void)

Transfer completed notification.

This notification occurs when a transfer is completed.

```

void retrieve_transfer_buffers_8(

REFERENCE_PARAM(uint8_t_movable_ptr_t,

buf), REFERENCE_PARAM(uint8_t_movable_ptr_t, outbuf),

)

```

Retrieve transfer buffers.

This function should be called after the *transfer\_complete()* notification and will return the buffers given to the other task by *init\_transfer\_array\_8()*.

#### **Parameters**

- ▶ inbuf A movable pointer that will be set to the buffer pointer that was filled during the transfer.

- outbuf A movable pointer that will be set to the buffer pointer that was transmitted during the transfer.

```

void retrieve_transfer_buffers_32(

REFERENCE_PARAM(uint32_t_movable_ptr_t, in-

buf), REFERENCE_PARAM(uint32_t_movable_ptr_t, outbuf),

)

```

Retrieve transfer buffers.

This function should be called after the *transfer\_complete()* notification and will return the buffers given to the other task by *init\_transfer\_array\_32()*.

#### **Parameters**

- ▶ inbuf A movable pointer that will be set to the buffer pointer that was filled during the transfer.

- outbuf A movable pointer that will be set to the buffer pointer that was transmitted during the transfer.

```

void set_ss_port_bit(unsigned device_index, unsigned ss_port_bit)

```

Sets the bit of port which is used for slave select (> 1b port type only) and only for spi\_master. spi\_master sets all bits in each port high/low

The default value (if this is not called) is the bit number is equal to the device\_index (0->0, 1->1 etc.).

#### **Parameters**

- device\_index The index of the device for which the port bit is to be set.

- ss\_port\_bit Which bit number in the port to use for slave select.

```

void set_miso_capture_timing(

unsigned

device_index, spi_master_miso_capture_timing_t

```

)

)

miso\_capture\_timing,

Configures the timing parameters for MISO capture. At frequencies above 20 MHz it is likely that some capture delays will need to be introduced to ensure setup and hold times are met.

See the following document for details on xcore.ai port timing: https://www. xmos.com/documentation/XM-014231-AN/html/rst/index.html

#### **Parameters**

- ▶ **device\_index** The index of the device for which the MISO timing is to be set.

- ▶ miso\_capture\_timing A structure of type spi\_master\_miso\_capture\_timing\_t with the desired settings.

#### void set\_ss\_clock\_timing(

unsigned device\_index, spi\_master\_ss\_clock\_timing\_t ss\_clock\_timing,

Configures the timing settings for SS assert to clock delay, and last clock to SS de-assert delay. The unit is reference timer ticks which is nominally 10 ns. The maximum setting is 65535 which equates to 655 us over which the setting will overflow back to zero.

#### **Parameters**

- ▶ device index The index of the device for which the SS timing is to be set.

- ▶ ss\_clock\_timing Α structure type spi\_master\_ss\_clock\_timing\_t with the desired settings.

#### void shutdown(void)

Shut down the SPI master interface server. Must be done after all transactions are complete to avoid leaving moveable pointers in the wrong place.

#### 13.2 Slave API

All SPI slave functions can be accessed via the spi.h header:

```

#include <spi.h>

```

You will also have to add lib\_spi to the APP\_DEPENDENT\_MODULES field of your application CMakefile.

#### 13.2.1 Creating an SPI slave instance

SPI slave component.

This function implements an SPI slave bus.

#### **Parameters**

- spi\_i The interface to connect to the user of the component. The component acts as the client and will make callbacks to the application.

- ▶ p\_sclk The SPI clock port.

- ▶ p\_mosi The SPI MOSI (master out, slave in) port.

- ▶ p\_miso The SPI MISO (master in, slave out) port.

- ▶ p\_ss The SPI SS (slave select) port.

- ▶ clk Clock to be used by the component.

- ▶ mode The SPI mode of the bus.

- ▶ transfer\_type The type of transfer the slave will perform: either SPI\_TRANSFER\_SIZE\_8 or SPI\_TRANSFER\_SIZE\_32.

# enum spi\_transfer\_type\_t

This type specifies the transfer size from the SPI slave component to the application

Values:

enumerator SPI\_TRANSFER\_SIZE\_8

Transfers should be 8-bit.

enumerator SPI\_TRANSFER\_SIZE\_32

Transfers should be 32-bit.

#### 13.2.2 The SPI slave interface API

#### group Spi\_slave\_callback\_if

This interface allows clients to interact with SPI slave tasks by completing call-backs that show how to handle data.

Methods for SPI slave interface

#### **Functions**

#### void master\_ends\_transaction(void)

This callback will get called when the master de-asserts on the slave select line to end a transaction.

#### uint32\_t master\_requires\_data(void)

This callback will get called when the master initiates a bus transfer or when more data is required during a transaction. The application must supply the data to transmit to the master. Data is transmitted with the least significant bit first. If the master completes the transaction before 8/32 bits (depending on SPI\_TRANSFER\_SIZE\_8 or SPI\_TRANSFER\_SIZE\_32) are transferred and the remaining bits are discarded.

#### **Returns**

the 8-bit or 32-bit value to transmit.

#### void master\_supplied\_data(uint32\_t datum, uint32\_t valid\_bits)

This callback will get called after a transfer. It will occur after every 8 bits transferred if the slave component is set to SPI\_TRANSFER\_SIZE\_8. If the component is set to SPI\_TRANSFER\_SIZE\_32 then it will occur if the master ends the transaction before 32 bits are transferred.

#### **Parameters**

- datum the data received from the master.

- valid\_bits the number of valid bits of data received from the master.

#### void request\_shutdown(void)

Request shut down the SPI slave interface client.

void shutdown\_complete(void)

Acknowledgment that the SPI slave task has been shutdown.

Copyright © 2025, All Rights Reserved.

XMOS Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS, XCORE, VocalFusion and the XMOS logo are registered trademarks of XMOS Ltd. in the United Kingdom and other countries and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.